“芯片大家说 I Say IC”第二十三期精彩回顾→芯来胡振波:RISC-V IP创新为本土带来独特价值

2024-06-28

芯来科技创始人 胡振波

处理器IP及与之密切相关的处理器指令集架构是整个集成电路产业上游最重要的核心部件,也是最为关键的底层技术。胡振波谈到,目前在处理器指令集架构领域,RISC-V已经与ARM、X86形成三分天下的趋势。相比于ARM和X86,RISC-V最大的优势和特点是其开放性。RISC-V是公开化的国际标准,它不从属于任何国家或任何一家公司,因此得到了广泛的产业支持,发展迅猛。

目前已经有大量的公司进入RISC-V领域,包括头部芯片设计公司、互联网巨头、芯片的创业公司等等。海外RISC-V领域更为火爆,欧美日韩企业都非常活跃。

开放标准下的生态格局将会是“自研”、“开源”与“中立解决方案提供商”共存的业态,这是专业化分工与经济模型的必然结果,能为行业带来最大化的经济效益。芯来选择作为中立解决方案提供商,只输出解决方案,不做芯片产品,保持中立,不与下游客户竞争。

芯来成立于2018年,定位于本土中立的RISC-V IP解决方案商,是国内本土RISC-V IP领军企业。自成立以来,芯来以年为度,保持稳健,发布了一系列的RISC-V IP产品。

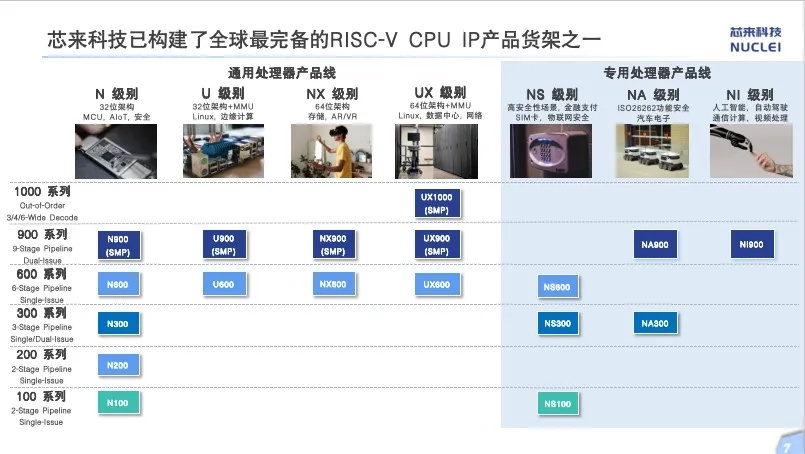

胡振波表示,IP公司与芯片产品公司发展思路不同,芯片产品公司需要时间打磨几款有竞争力的芯片产品,而IP公司更像是“货架”。芯片产品形态多样,对IP的要求也就更多样化。IP的丰富度是IP公司实力的重要指标。

目前,芯来已构建了完备的RISC-V IP产品线。今年发布的1000系列更是主打高性能,应用场景适配于高性能自动驾驶、通信网络、数据中心与人工智能领域等。应用于IoT、MCU、工控的300系列是客户数量最多的产品线。NA900系列是国际第一个RISC-V 架构下获得ISO26262 ASIL-D产品认证的IP产品。

胡振波认为,相比于海外芯片设计的成熟业态,国内芯片设计业格局碎片化,企业众多,活跃的芯片设计公司也有几百家,市场空间广阔。但其不确定性也更强,需要IP厂商快速响应。

传统CPU IP授权模式运行了30多年,在国际国内都非常普遍。这种IP授权1.0模式的若干痛点凸显:获取门槛高,对于不同应用的不同IP都需单独申请与评估;每个项目都要单独的授权费;决策成本高,使得芯片项目的立项与选型决策成本高;商务法务流程长,每个项目商务法务都需要冗长的流程。这需要更加灵活便捷的商业模式来解决上述痛点。

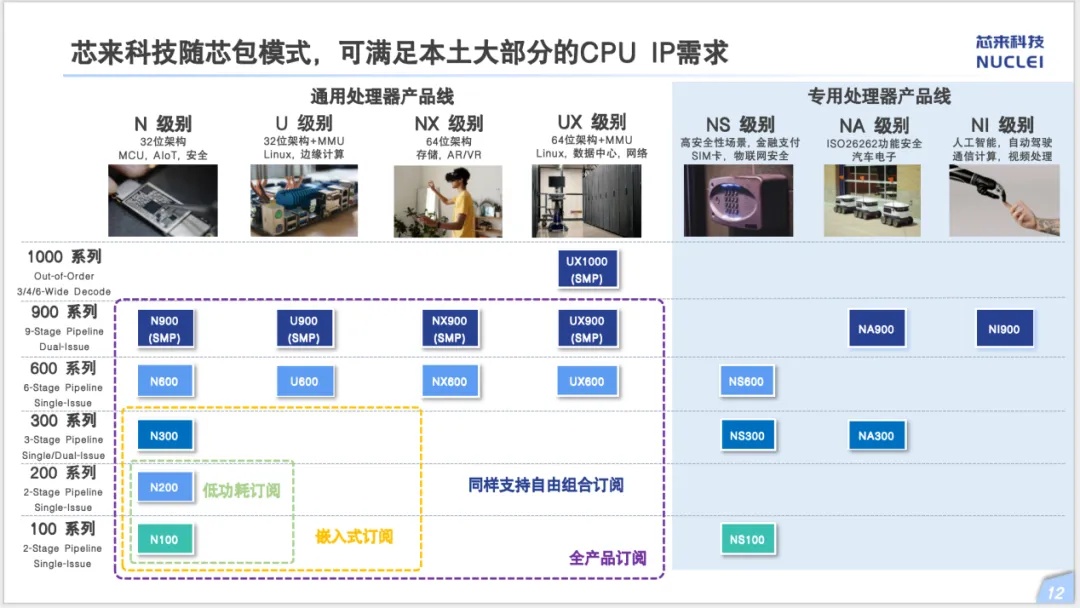

今年芯来科技首次推出RISC-V IP “随芯包”模式,将传统按项目授权转变为订阅模式,大幅缩减CPU IP的授权成本和授权过程。随芯包模式带给客户极大的便利性和灵活性,订阅期内客户可无限次使用随芯包内IP,可以根据自身需求选择订阅内容,订阅期内实时享有IP特性和工具链的升级,以及技术支持。

IP的采购方多为芯片SoC设计企业。在大量的合作案例中,芯来也发现了本土SoC设计领域的痛点。相比于海外成熟业态,本土市场较为碎片化,项目节奏越来越快,SoC定制性与时效性强,Time-to-Market要求很高。传统模式下,采用的是分离IP授权模式。而目前尤其是本土芯片项目方普遍面临着资金紧张、时间紧张、人力不足三方面的压力。他们需要花大量精力采购或自研周边的其他IP,还需要在SoC集成与复杂验证上投入大量人力,同时SoC集成与验证周期长,时间成本高昂。

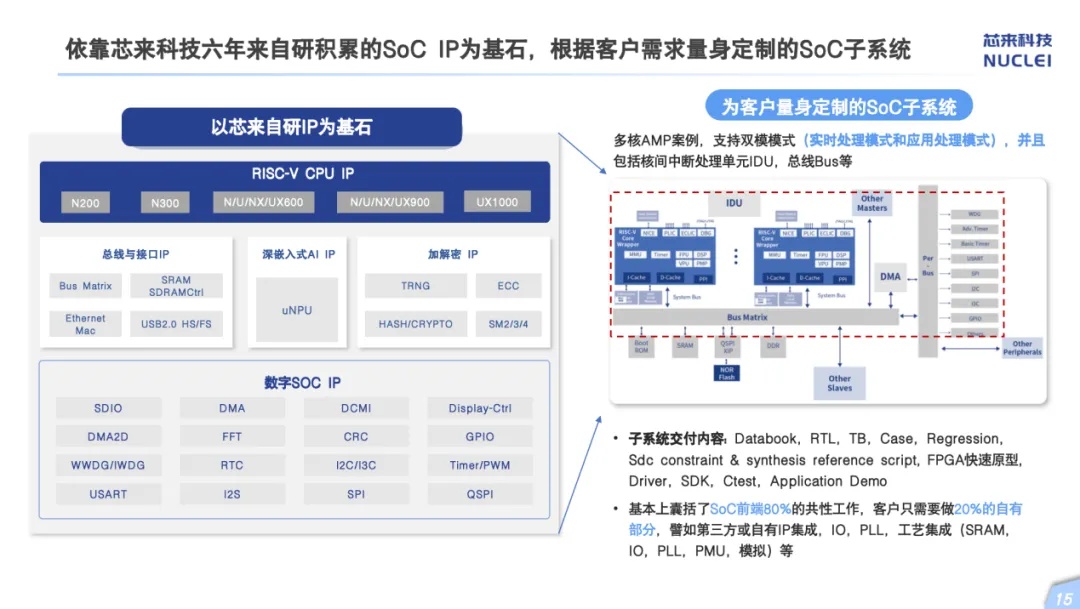

为解决这一问题,芯来科技以六年来自研积累的通用SoC IP为基石,根据客户需求量身定制推出SoC子系统服务,可以解决80%共性问题,极大减少SoC前端设计工作量与成本。在子系统IP模式基础上,芯来推出了面向AI、HSM和车规的垂直解决方案。

利用CPU子系统IP模式,芯来可服务各类型的芯片项目方,包括系统公司、设计服务公司、SoC产品公司与中小型创业公司。

胡振波将CPU IP随芯包与子系统解决方案称为RISC-V IP2.0模式。通过大幅缩减CPU IP的授权成本和大幅降低SoC前端精力和成本,芯来助力本土设计公司更高效地完成CPU IP的授权过程,加速本土芯片设计企业产品上市进程,赋能本土集成电路产业升级。